SiC器件测试回路杂散电感优化方法

1、概述

近年来,以碳化硅(Silicon Carbide,SiC)材料为代表的宽禁带功率器件,受到电力能源行业的广泛关注。与基于传统硅(Silicon,Si)材料器件相比,SiC 器件具有耐高压、耐高温、开关速度快,损耗低等优点,在高效率、高功率密度应用场景具有明显优势。但较大的 di /dt 使电路中的杂散电感产生瞬时的电压冲击,不仅减少了功率开关的使用寿命、增加了功耗,甚至可能会击穿器件。另外,对整个系统 而言,电压过冲还会使电路输出谐波增加,造成严重的电磁干扰。

在整个功率模块拓扑结构中,杂散电感主要由PCB母排电感、支撑电容杂散电感、功率器件杂散电感以及连接螺柱的等效电感组成。其中,器件的杂散电感有器件物理结构和布局决定,支撑电容的杂散电感主要有所选用的电容主导。作为器件和应用接口的PCB母排的杂散电感设计,是降低线路杂散电感的重要途径除了PCB母排的电感,其余,其大小与厂商的生产工艺有关,所以设计出低感的PCB母排结构,是降低线路杂散电感的重要途径。

2、影响PCB母排杂散电感的因素

2.1 焊盘大小对杂散电感的影响

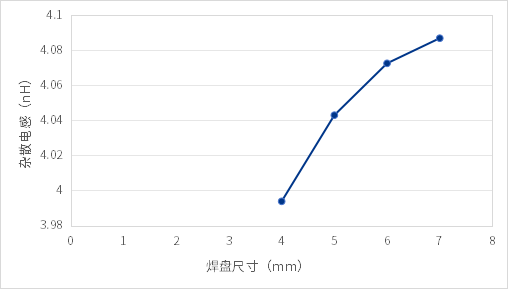

电容焊盘大小分别设置为4、5、6、7mm四个不同直径,通过ANSYSQ3D软件对不同条件进行仿真,其结果如图1所示。

图1 焊盘大小对杂散电感的影响

因为layout时爬电距离设计相同,在其他限制条件相同的情况下,焊盘大小的差异本质上就是导体宽度的大小差异,可以看出导体宽度越宽杂散电感越小。较宽的导体可以减少电阻,同时减少了导体间的磁场耦合,从而降低杂散电感。因此使用宽而扁平的导体代替细长的导体可以有效减少杂散电感。

2.2 层间距对杂散电感的影响

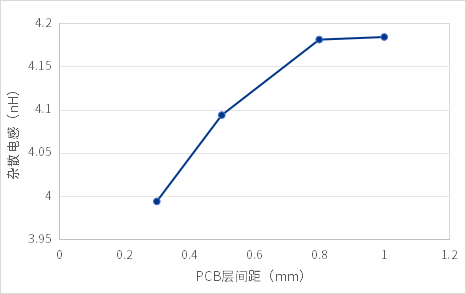

在对层间距为变量的仿真中,保持其他限制条件全部相同的情况下,分别对0.3、0.5、0.8、1.0四种不同层间距下的杂散电感数据仿真结果如图2所示。

图2 层间距对杂散电感的影响

从仿真结果可知,导体之间的距离越近,形成的磁场相互作用越强,杂散电感越小。因此,在保证爬电安全距离的前提下,尽可能的减小导体间的距离有助于降低杂散电感。

2.3 过孔对杂散电感的影响

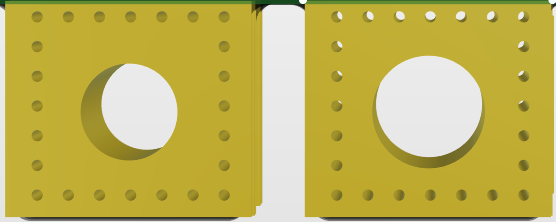

过孔的数量和分布会影响电流的分布和路径。合理设计过孔可以减少电流路径的长度,从而降低杂散电感。图3和4分别为有过孔和无过孔示意图。

图3 有过孔示意图

图4 无过孔示意图

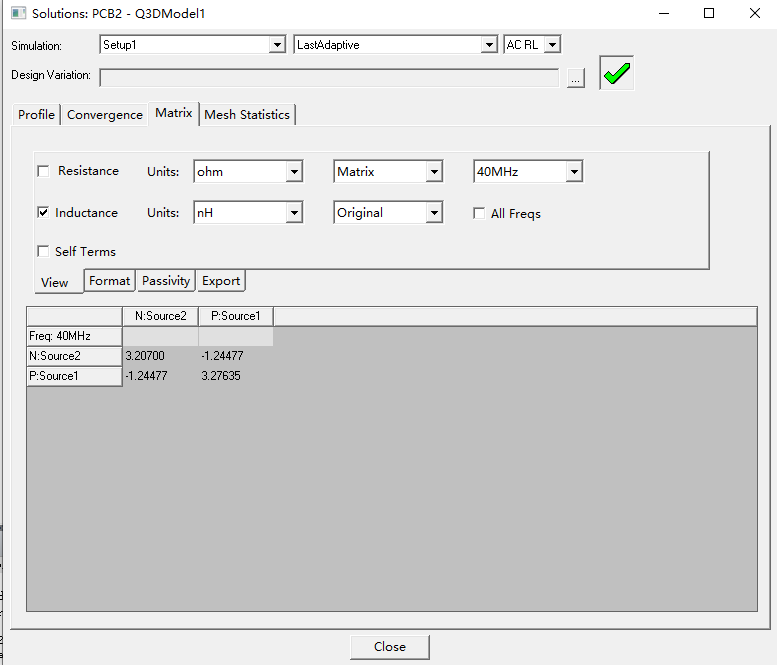

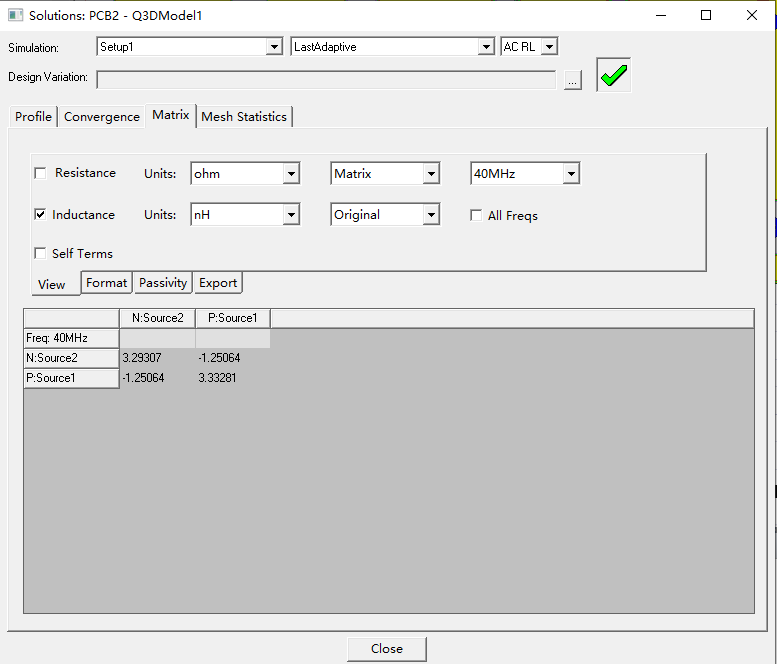

图5与图6分别为有过孔的杂散电感仿真数据和无过孔的杂感仿真数据。

图5 有过孔杂散电感仿真数据

图6 无过孔杂散电感仿真数据

由图5数据计算得有过孔时杂散电感仿真数据为3.99nH,由图6数据计算得无过孔时杂散电感仿真数据为4.12nH。使用多个过孔并联可以减少单个过孔的阻抗,提高电流分布的均匀性,所以可以通过合理使用过孔达到降低杂散电感的目的。

3、小结

本文针对PCB叠层母排导体宽度、导体的层间距、过孔等因素对杂散电感的影响做了详细的仿真与分析。分析了不同因素对杂散电感的影响及其原因,提出了基于改善电流流通通道实现杂散电感优化的方法:

1.使用宽而扁平的导体代替细长的导体;

2.在保证爬电安全距离的前提下,尽可能的减小导体间的距离;

3.合理使用过孔。

参考文献

[1] 何寒冰.叠层母排在矿用变频器中的设计研究[J].煤矿机电,2022,43(3) :68-71,82.doi:10.16545 /j.Cnki.Cmet.2022.03.016

[2] 朱艺锋,郑景乐.基于结构的变流器母排杂散电感优化方法研究[J].机电工程, 2017, 34(3):5.DOI:10.3969/j.issn.1001-4551.2017.03.016.

[3] 於少林,张兴,王佳宁*,吴馥晨,王琛,刘元剑.基于分立器件并联型碳化硅逆变器的叠层母排设计研究.中国电机工程学报, 2022.5.20, 42(10).DOI: 10.13334/j.0258-8013.pcsee.211449