栅极电压对功率半导体器件测试的影响

1、概述

实际应用中,功率半导体器件的开关特性受栅极电压的影响,所以实际的开关特性与数据手册描述的特性会存在一定的差异。因此,有必要研究栅极电压对功率半导体的影响,本文将搭建动态测试平台,通过双脉冲测试和短路测试验证不同栅极电压对不同种类器件的影响。

2.功率半导体器件测试方法

2.1 测试环境搭建

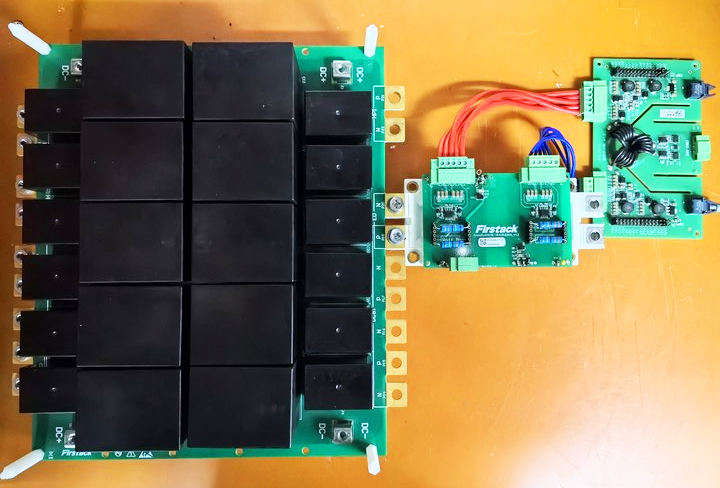

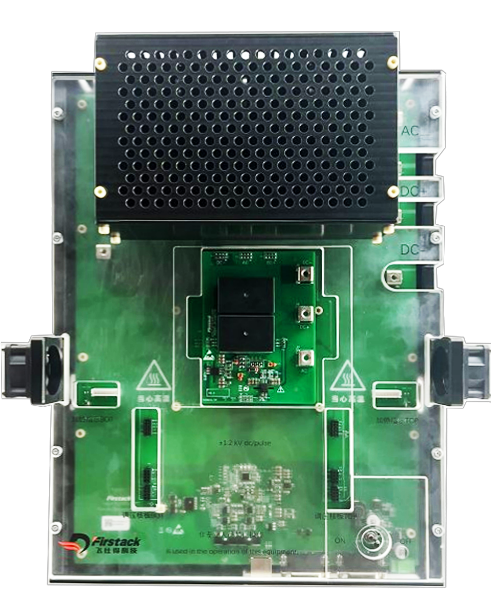

测试设备:Firstack的动态测试设备ME300D、模块测试工装、单管测试工装

测试模块:英飞凌器件FF450R12ME4、英飞凌器件IMZA120R008M1H

图1 Firstack动态特性测试设备ME300D

图2 Firstack模块测试工装

图3 Firstack单管测试工装

2.2 测试数据及波形分析

2.2.1. IGBT器件(FF450R12ME4)

短路测试 | 测试数据 | 测试条件 | VGE(+)=+15V | VGE(+)=+16V |

Vset(V) | VCE=300V t=6us VGE(-)=-15V | 300 | 300 | |

Vgemax(V) | 15.094 | 16.066 | ||

Vcemax(V) | 519.828 | 533.953 | ||

Icmax(A) | 1893.828 | 2221.844 | ||

Esc(uJ) | 2288659.226 | 2661123.895 | ||

| ||||

双脉冲测试 | 测试数据 | 测试条件 | VGE(-)=-15V | VGE(-)=-1V |

Vset(V) | VCE=200V IC=100A VGE(+)=+15V | 200 | 200 | |

Ic(A) | 99.316 | 100.496 | ||

Vcemax(V) | 238.867 | 243.313 | ||

tdoff(ns) | 453.76 | 988.16 | ||

tf(ns) | 273.68 | 297.6 | ||

dv/dt(off)(V/us) | 2111.564 | 2252.546 | ||

di/dt(off)(A/us) | 302.412 | 289.17 | ||

tdon(ns) | 139.52 | 109.44 | ||

tr(ns) | 53.76 | 51.84 | ||

dv/dt(on)(V/us) | 958.633 | 975.233 | ||

di/dt(on)(A/us) | 2282.498 | 2326.606 | ||

表1 IGBT器件测试数据

分析:在栅极耐压极限内,将IGBT器件栅极正压从+15V提升到+16V,短路电流增加了17.3%,短路损耗增加了16.3%;将IGBT器件栅极负压从-15V提升到-1V,tdon减少21.6%,tdoff增加117.8%。

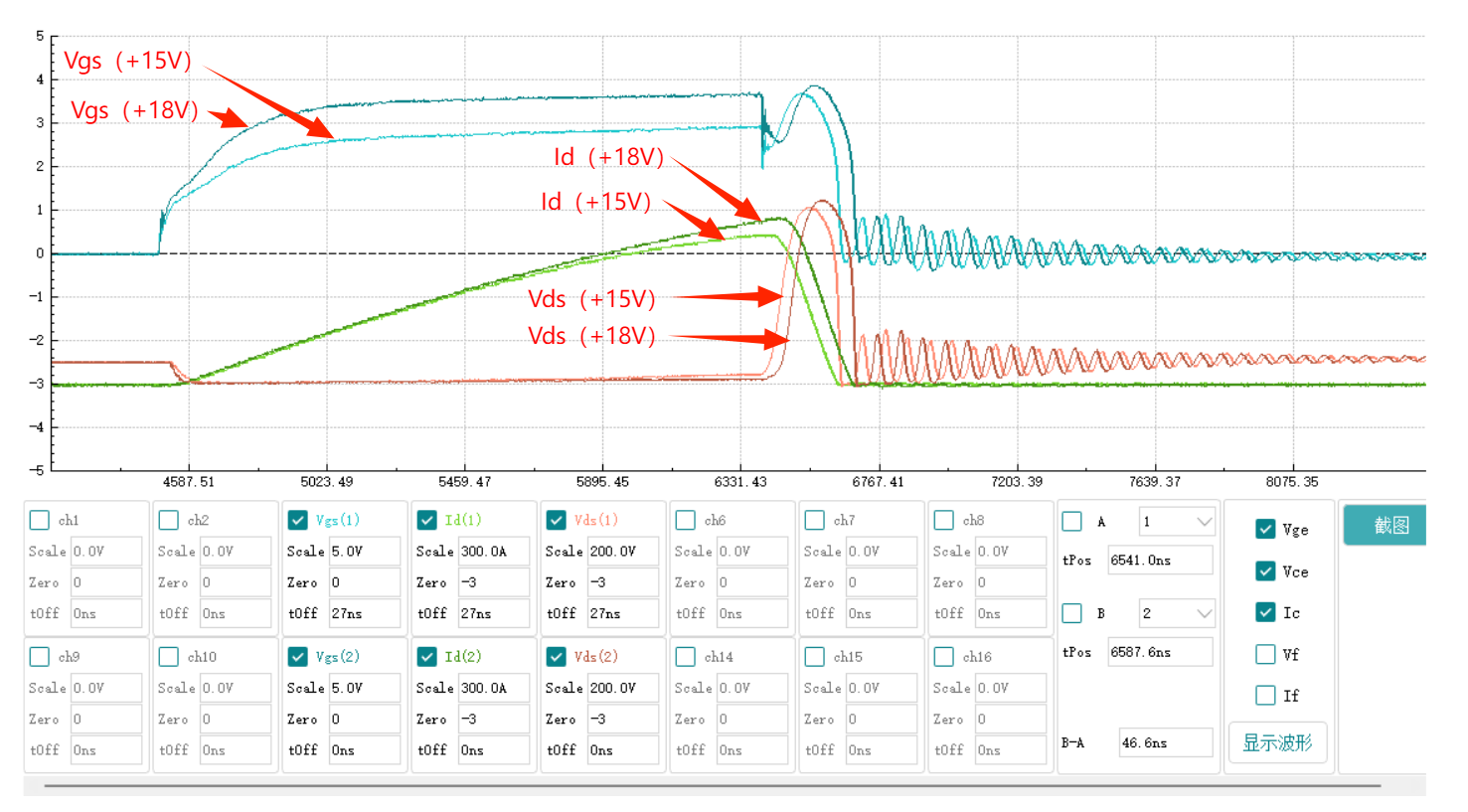

使用DPowerAnalysis叠图工具,得到如下波形。

图4 短路测试波形叠图

分析:在栅极耐压极限内,将IGBT器件栅极正压从+15V提升到+16V,从叠图波形上观察,短路电流明显增加。

图5 一次关断波形叠图

分析:将IGBT器件栅极负压从-15V提升到-1V,关断产生572.7ns的延迟。

2.2.2. SiC MOSFET器件(IMZA120R008M1H)

短路测试 | 测试数据 | 测试条件 | VGS(+)=+15V | VGS(+)=+18V |

Vset(V) | VDS=100V t=2us VGS(-)=0V | 100 | 100 | |

Vgsmax(V) | 18.6 | 19.2 | ||

Vdsmax(V) | 816 | 840 | ||

Idmax(A) | 1032 | 1140 | ||

Esc(uJ) | 96068.905 | 101828.951 | ||

| ||||

双脉冲测试 | 测试数据 | 测试条件 | VGS(-)=-3V | VGS(-)=0V |

Vset(V) | VDS=200V IC=20A VGS(+)=+18V | 200 | 200 | |

Id(A) | 19.569 | 19.469 | ||

Vdsmax(V) | 229.891 | 231.211 | ||

tdoff(ns) | 76.8 | 96.8 | ||

tf(ns) | 28 | 36.8 | ||

dv/dt(off)(V/us) | 7277.902 | 5935.791 | ||

di/dt(off)(A/us) | 414.129 | 322.458 | ||

tdon(ns) | 28.8 | 22.4 | ||

tr(ns) | 27.2 | 28 | ||

dv/dt(on)(V/us) | 5899.816 | 5766.518 | ||

di/dt(on)(A/us) | 2243.75 | 2216.518 | ||

表2 SiC MOSFET器件测试数据

分析:在栅极耐压极限内,将SiC MOSFET器件规格书推荐栅极正压从+15V提升到+18V,短路电流增加了3.1%,短路损耗增加了5.7%;将SiC MOSFET器件栅极负压从-3V提升到0V,tdon减少28.6%,tdoff增加20.7%,tf增加31.4%,dv/dt(off)减少22.6%,di/dt(off)减少28.4%。

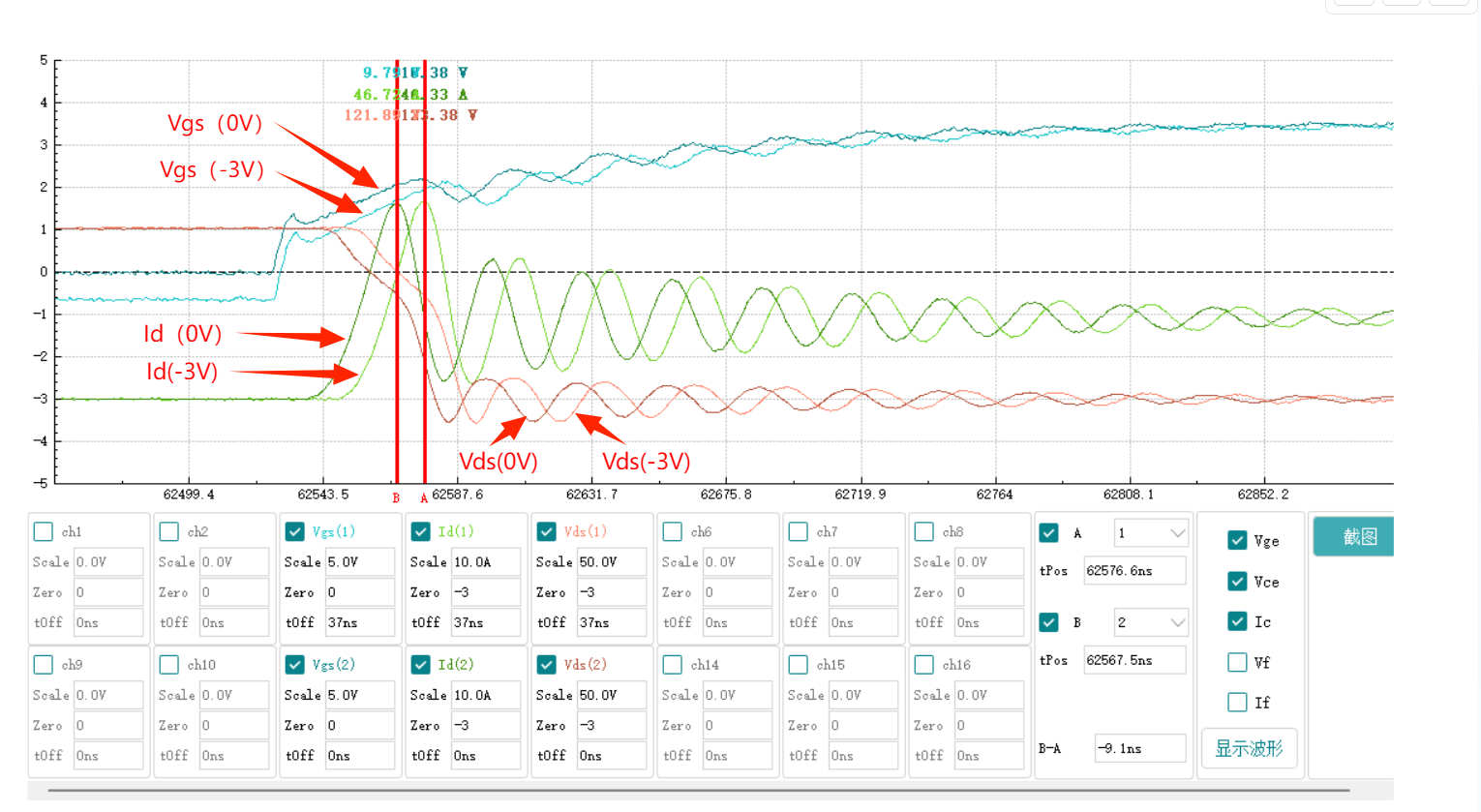

使用DPowerAnalysis叠图工具,得到如下波形。

图6 短路测试波形叠图

分析:在栅极耐压极限内,将SiC MOSFET器件栅极正压从+15V提升到+18V,从叠图波形上观察,短路电流明显增加。

图7 一次关断波形叠图

分析:将SiC MOSFET器件栅极负压从-3V提升到0V,关断产生32.6ns的延迟。

3.小结

根据上述测试结果可以分析出,IGBT和SiC MOSFET器件对于栅极电压变化产生的影响有一定差别:

1)将栅极正压提高,IGBT和SiC MOSFET器件的短路电流和损耗增加、延时加大,但SiC MOSFET器件所受的影响要小于IGBT器件。

2)将栅极负压提高,IGBT和SiC MOSFET器件的关断变慢,由于SiC MOSFET的开通关断速度高于IGBT,故SiC MOSFET延迟时间明显小于IGBT。

对于不同种类的功率半导体器件,最适合的栅极电压配置不一样。可以借助动态测试设备评估不同栅极电压对于器件的影响,结合器件规格书和实际使用环境,选定最适合的栅极参数。